## Using uM-FPU V3.1 with the BasicATOM

## Introduction

The uM-FPU V3.1 chip is a 32-bit floating point coprocessor that can be easily interfaced with the BasicATOM microcontrollers from Basic Micro, to provide support for 32-bit IEEE 754 floating point operations and 32-bit long integer operations. The uM-FPU V3.1 chip supports both I<sup>2</sup>C and SPI connections.

This document describes how to use the uM-FPU V3.1 chip with the BasicATOM. For a full description of the uM-FPU V3.1 chip, please refer to the *uM-FPU V3.1 Datasheet* and *uM-FPU V3.1 Instruction Reference*. Application notes are also available on the Micromega website.

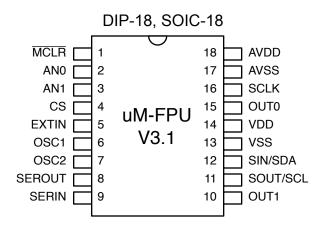

## uM-FPU V3.1 Pin Diagram and Pin Description

| Pin | Name        | Type            | Description                                          |

|-----|-------------|-----------------|------------------------------------------------------|

| 1   | /MCLR       | Input           | Master Clear (Reset)                                 |

| 2   | AN0         | Input           | Analog Input 0                                       |

| 3   | AN1         | Input           | Analog Input 1                                       |

| 4   | CS          | Input           | Chip Select, Interface Select                        |

| 5   | EXTIN       | Input           | External Input                                       |

| 6   | OSC1        | Input           | Oscillator Crystal (optional)                        |

| 7   | OSC2        | Output          | Oscillator Crystal (optional)                        |

| 8   | SEROUT      | Output          | Serial Output, Debug Monitor - Tx                    |

| 9   | SERIN       | Input           | Serial Input, Debug Monitor - Rx                     |

| 10  | OUT1        | Output          | Digital Output 1                                     |

| 11  | SOUT<br>SCL | Output<br>Input | SPI Output, Busy/Ready Status I <sup>2</sup> C Clock |

| 12 | SIN<br>SDA | Input<br>In/Out | SPI Input<br>I <sup>2</sup> C Data |

|----|------------|-----------------|------------------------------------|

| 13 | VSS        | Power           | Digital Ground                     |

| 14 | VDD        | Power           | Digital Supply Voltage             |

| 15 | OUT0       | Output          | Digital Output 0                   |

| 16 | SCLK       | Input           | SPI Clock                          |

| 17 | AVSS       | Power           | Analog Ground                      |

| 18 | AVDD       | Power           | Analog Supply Voltage              |

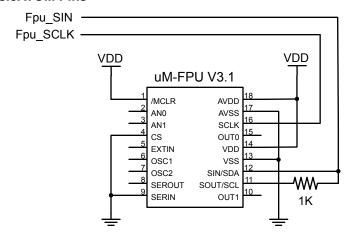

## Connecting the BasicATOM using 2-wire SPI

Only two pins are required for interfacing a BasicATOM to the uM-FPU V3.1 chip using a 2-wire SPI interface. The communication uses a bidirectional serial interface that requires a clock pin and a data pin. An example of the pin settings for the BasicATOM are shown below. (They can be changed to suit your application.)

```

Fpu_SCLK con P0 ' SPI SCLK pin

Fpu_SIN con P1 ' SPI MOSI (connected to FPU SIN)

Fpu_SOUT con P1 ' SPI MISO (same pin as FPU SIN)

' Fpu Wait monitors IN1 pin

```

## **SPI 2-wire Connection Diagram**

#### **BasicATOM Pins**

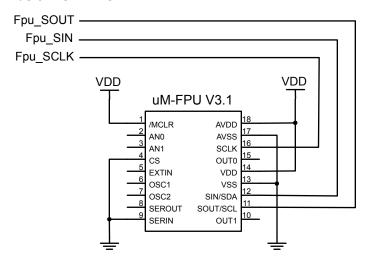

## Connecting the BasicATOM using 3-wire SPI

Three pins are required for interfacing a BasicATOM to the uM-FPU V3.1 chip using a 3-wire SPI interface. The communication uses a clock pin, an input data pin, and an output data pin. An example of the pin settings for the BasicATOM are shown below. (They can be changed to suit your application.)

```

Fpu_SCLK con P0 ' SPI SCLK (connected to uM-FPU SCLK pin)

Fpu_SIN con P1 ' SPI MOSI (connected to uM-FPU SIN/SDA pin, 1K resistor)

Fpu_SOUT con P2 ' SPI MISO (connected to uM-FPU SIN/SDA pin, 1K resistor)

' Fpu Wait monitors IN2 pin

```

## **SPI 3-wire Connection Diagram**

## **BasicATOM Pins**

## Connecting the BasicATOM using I<sup>2</sup>C

The uM-FPU V3.1 can also be connected using an I<sup>2</sup>C interface. The default slave ID for the uM-FPU chip is \$C8. An example of the pin settings for the BasicATOM are shown below (they can be changed to suit your application):

```

Fpu_SCLK con P0 ' I2C SCL pin (connected to FPU SOUT/SCL)

Fpu SIN con P1 ' I2C SDA pin (connected to FPU SIN/SDA)

```

#### I<sup>2</sup>C Connection Diagram VDD **BasicATOM Pins** Fpu SCL Fpu\_SDA **VDD** VDD uM-FPU V3.1 Note: SCL and SDA must have pull-up /MCLR AVDD resistors as required AN0 AVSS by the I2C bus. AN1 SCLK OUT0 CS **EXTIN** VDD OSC1 VSS OSC2 SIN/SDA SEROUT SOUT/SCL SERIN OUT1

## Brief Overview of the uM-FPU V3.1 Floating Point Coprocessor

For a full description of the uM-FPU V3.1 chip, please refer to the uM-FPU V3.1 Datasheet, uM-FPU V3.1 Instruction Reference. Application notes are also available on the Micromega website.

The uM-FPU V3.1 chip is a separate coprocessor with its own set of registers and instructions designed to provide microcontrollers with 32-bit floating point and long integer capabilities. The BasicATOM communicates with the FPU using an SPI or I<sup>2</sup>C interface. Instructions and data are sent to the FPU, and the FPU performs the calculations. The BasicATOM is free to do other tasks while the FPU performs calculations. Results can be read back to the BasicATOM or stored on the FPU for later use. The uM-FPU V3.1 chip has 128 registers, numbered 0 through 127, that can hold 32-bit floating point or long integer values. Register 0 is often used as a temporary register and is modified by some of the uM-FPU V3.1 instructions. Registers 1 through 127 are available for general use.

The SELECTA instruction is used to select any one of the 128 registers as register A. Register A can be regarded as an accumulator or working register. Arithmetic instructions use the value in register A as an operand and store the result of the operation in register A. If an instruction requires more than one operand, the additional operand is specified by the instruction. The following example selects register 2 as register A and adds register 5 to it:

```

SELECTA, 2 select register 2 as register A

FADD, 5 register[A] = register[A] + register[5]

```

## **Reserved Words**

The BasicATOM has several reserved words that are the same as uM-FPU opcode definitions. To avoid these reserved words, the following uM-FPU opcodes have been defined with a F prefix:

| F_SIN  | $F\_FLOAT$ |

|--------|------------|

| F_COS  | F_SYNC     |

| F_SWAP | F_SEROUT   |

| F GOTO | F SERIN    |

## Using the SPI Interface to communicate with the uM-FPU

Appendix A contains a table that gives a summary of each uM-FPU V3.1 instruction, with enough information to follow the examples in this document. For a detailed description of each instruction, refer to the *uM-FPU V3.1 Instruction Reference*.

## Using the shiftout and shiftin commands

The shiftout command is used to write instructions and data to the FPU using an SPI interface.

The shiftin command is used to read data from the FPU using an SPI interface.

A couple of issues must be accounted for when using the shiftin and shiftout commands.

Issue (as of Basic Micro Studio 1.0.0.15):

Variables with more than 16 bits (e.g. long) don't transmit properly.

Workaround:

Long values must be transmitted as two 16-bit values.

e.g. Instead of longval\32 use longval.highbyte\16, longval.lowbyte\16

#### Issue:

The float data type can't be used with the shiftin or shiftout command.

#### Workaround:

A long alias can be defined for floating point variables. The long alias can then be used to read and write the floating point value. The following example writes the value in floating point variable x to the FPU.

```

x var float

ix var tmp.long

shiftout Fpu SIN, Fpu SCLK, FASTMSBPRE,[FWRITEA, ix.hiqhByte\16, ix.lowByte\16]

```

The Basic Micro uses a slightly different format then the IEEE 754 format used internally by the FPU, but the FPU can be set to automatically translate between the two formats when reading and writing floating point values. A mode bit can be set on the FPU so that the alternate PIC format is automatically selected at reset, or the PICMODE instruction can be used to set the FPU for the alternate PIC format. In most applications, floating point values are left on the FPU and integer values are transmitted back and forth.

All instructions have an opcode that tells the FPU which operation to perform. The following example calculates the square root of register A:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SQRT]

```

Some instructions require additional operands or data and are specified by the bytes following the opcode. The following example adds register 5 to register A.

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [F_FADD, 5]

```

Some instructions return data. This example reads the lower 8 bits of register A:

```

gosub Fpu_Wait

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LREADBYTE]

gosub Fpu_ReadDelay

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [dataByte]

```

The following example adds the value in register 5 to the value in register 2.

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SELECTA, 2, F_FADD, 5]

```

It's a good idea to use constant definitions to provide meaningful names for the registers. This makes your program easier to read and understand. The same example using constant definitions would be:

```

Total CON 2 'total amount (uM-FPU register)

Count CON 5 'current count (uM-FPU register)

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SELECTA, Total, F_FADD, Count]

```

## Using the I<sup>2</sup>C Interface to communicate with the uM-FPU

Appendix A contains a table that gives a summary of each uM-FPU V3.1 instruction, with enough information to follow the examples in this document. For a detailed description of each instruction, refer to the *uM-FPU V3.1 Instruction Reference*.

## Using the i2cout and i2cin commands

The i2cout command is used to write instructions and data to the FPU using an I<sup>2</sup>C interface.

The i2cin command is used to read data from the FPU using an I<sup>2</sup>C interface.

All data output by the i2cout command and input by the i2cin command is 8-bit.

A couple of issues must be accounted for when using the i2cin and i2cout commands.

#### Issue:

The FPU I<sup>2</sup>C interface uses two write registers and two read registers. When using the i2cout command the register number must always be specified as the first byte of the transfer.

#### Solution:

Since the i2cout commands in a user program always access the I<sup>2</sup>C data register (I<sup>2</sup>C register 0), just add a zero as the first byte of any transfer. For example, to send the SELECTA, 1 instruction, the following i2cout command would be used:

```

i2cout Fpu SDA, Fpu SCL, Fpu ID, [0, SELECTA, 1]

```

#### Issue:

The float data type can't be used with the i2cin or i2cout command.

#### Solution:

A long alias can be defined for floating point variables. The long alias can then be used to read and write the floating point value. The following example writes the value in floating point variable x to the FPU.

```

x var float

ix var x.long

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, FWRITEA, ix.byte3, ix.byte2, ix.byte1.

ix.byte0]

```

The Basic Micro uses a slightly different format then the IEEE 754 format used internally by the FPU, but the FPU can be set to automatically translate between the two formats when reading and writing floating point values. A mode bit can be set on the FPU so that the alternate PIC format is automatically selected at reset, or the PICMODE instruction can be used to set the FPU for the alternate PIC format. In most applications, floating point values are left on the FPU and integer values are transmitted back and forth.

All instructions have an opcode that tells the FPU which operation to perform, The following example calculates the square root of register A:

```

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SQRT]

```

Some instructions require additional operands or data and are specified by the bytes following the opcode. The following example adds register 5 to register A.

```

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, F_FADD, 5]

```

Some instructions return data. This example reads the lower 8 bits of register A:

```

gosub Fpu_Wait

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, LREADBYTE]

gosub Fpu_ReadDelay

i2cin Fpu_SDA, Fpu_SCL, Fpu_ID, [dataByte]

```

The following example adds the value in register 5 to the value in register 2.

```

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SELECTA, 2, F_FADD, 5]

```

It's a good idea to use constant definitions to provide meaningful names for the registers. This makes your program easier to read and understand. The same example using constant definitions would be:

```

Total CON 2 ' total amount (uM-FPU register)

Count CON 5 ' current count (uM-FPU register)

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SELECTA, Total, F_FADD, Count]

```

## uM-FPU V3.1 Support Software

There are two include files that provide all of the support routines for interfacing to the BasicATOM with the uM-FPU V3.1 chip. The fpuv3-spi.bas file provides SPI support and the fpuv3-i2c.bas provides I<sup>2</sup>C support. One of these files must be included at the start of the program. Several sample applications are also included with the support files.

SPI:

```

#include "C:\My BasicATOM\fpuv3-spi.bas"

PC:

#include "C:\My BasicATOM\fpuv3-i2c.bas"

Issue: (as of Basic Atom Studio 1.0.0.15)

```

There's a problem with the #include statement generating the wrong path.

Workaround:

Specify the full pathname for the include file.

## Fpu\_Reset

To ensure that the BasicATOM and the FPU are synchronized, a reset call must be done at the start of every program. The Fpu\_Reset routine resets the FPU, confirms communications, and returns the sync character (\$5C) in the fpu\_status variable if the reset is successful.

## Fpu\_Wait

The FPU must have completed all instructions in the instruction buffer, and be ready to return data, before sending an instruction to read data from the FPU. The Fpu\_Wait routine checks the ready status of the FPU and waits until it is ready. The print routines check the ready status, so calling Fpu\_Wait before calling a print routine isn't required, but if your program reads directly from the FPU using the shiftin or i2cin commands, a call to Fpu\_Wait must be made prior to sending the read instruction. An example of reading a byte value is as follows: SPI:

```

gosub Fpu_wait

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LREADBYTE]

gosub Fpu_ReadDelay

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [dataByte]

FC:

gosub Fpu_wait

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, LREADBYTE]

gosub Fpu_ReadDelay

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, dataByte]

```

#### Description:

- wait for the FPU to be ready

- send the LREADBYTE instruction

- read a byte value and store it in the variable dataByte

The uM-FPU V3.1 chip has a 256 byte instruction buffer. In most cases, data will be read back before 256 bytes have been sent to the FPU. If a long calculation is done that requires more than 256 bytes to be sent to the FPU, an Fpu\_Wait call should be made at least every 256 bytes to ensure that the instruction buffer doesn't overflow.

## Fpu\_ReadStatus

The current status byte is read from the FPU and returned in the fpu status variable.

## Fpu\_ReadDelay

After a read instruction is sent, and before the first data is read, a setup delay is required to ensure that the FPU is ready to send data. The Fpu\_ReadDelay routine provides the required read setup delay. The delay is only required before the first byte read after a read instruction.

#### **Print Version**

The FPU version string is sent to the terminal using the serout command.

## Print\_Float

The value in register A is sent to the terminal as a floating point string using the serout command. Up to eight significant digits will be displayed if required. Very large or very small numbers are displayed in exponential notation. The length of the displayed value is variable and can be from 3 to 12 characters in length. The special cases of NaN (Not a Number), +Infinity, -Infinity, and -0.0 are handled. Examples of the display format are as follows:

| 1.0        | NaN       | 0.0  |

|------------|-----------|------|

| 1.5e20     | Infinity  | -0.0 |

| 3.1415927  | -Infinity | 1.0  |

| -52.333334 | -3.5e-5   | 0.01 |

## Print\_FloatFormat

The value in register A is sent to the terminal as a formatted floating point string using the serout command. The format variable is used to specify the desired format. The tens digit specifies the total number of characters to display and the ones digit specifies the number of digits after the decimal point. If the value is too large for the format specified, then asterisks will be displayed. If the number of digits after the decimal points is zero, no decimal point will be displayed. Examples of the display format are as follows:

| Value in A register | format   | Display format |

|---------------------|----------|----------------|

| 123.567             | 61 (6.1) | 123.6          |

| 123.567             | 62 (6.2) | 123.57         |

| 123.567             | 42 (4.2) | * • * *        |

| 0.9999              | 20 (2.0) | 1              |

| 0.9999              | 31 (3.1) | 1.0            |

## Print\_Long

The value in register A is sent to the terminal as a signed long integer string using the serout command. The displayed value can range from 1 to 11 characters in length. Examples of the display format are as follows:

## Print\_LongFormat

The value in register A is sent to the terminal as a formatted long integer string using the serout command. The format variable is used to specify the desired format. A value between 0 and 15 specifies the width of the display field for a signed long integer. The number is displayed right justified. If 100 is added to the format value the value is displayed as an unsigned long integer. If the value is larger than the specified width, asterisks will be displayed. If the width is specified as zero, the length will be variable. Examples of the display format are as follows:

| Value in register A | form | at            | Display format |

|---------------------|------|---------------|----------------|

| -1                  | 10   | (signed 10)   | -1             |

| -1                  | 110  | (unsigned 10) | 4294967295     |

| -1                  | 4    | (signed 4)    | -1             |

| -1                  | 104  | (unsigned 4)  | ***            |

| 0                   | 4    | (signed 4)    | 0              |

| 0                   | 0    | (unformatted) | 0              |

| 1000                | 6    | (signed 6)    | 1000           |

## Print\_FpuString

The contents of the FPU string buffer are sent to the terminal using the serout command.

## **Loading Data Values to the FPU**

Most of the data read from devices connected to the BasicATOM will return some type of integer value. There are several ways to load integer values to the FPU and convert them to 32-bit floating point or long integer values.

## 8-bit Integer to Floating Point

The FSETI, FADDI, FSUBI, FSUBRI, FMULI, FDIVI, FDIVRI, FPOWI, and FCMPI instructions read the byte following the opcode as an 8-bit signed integer, convert the value to floating point, and then perform the operation. It's a convenient way to work with constants or data values that are signed 8-bit values. The following example stores the lower 8 bits of variable dataByte to the Result register on the FPU.

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SELECTA, Result, FSETI, dataByte]

FC:

i2cout Fpu SDA, Fpu SCL, Fpu ID, [0, SELECTA, Result, FSETI, dataByte]

```

The LOADBYTE instruction reads the byte following the opcode as an 8-bit signed integer, converts the value to floating point, and stores the result in register 0.

The LOADUBYTE instruction reads the byte following the opcode as an 8-bit unsigned integer, converts the value to floating point, and stores the result in register 0.

## 16-bit Integer to Floating Point

The LOADWORD instruction reads the two bytes following the opcode as a 16-bit signed integer (MSB first), converts the value to floating point, and stores the result in register 0. The following example adds the lower 16 bits of variable dataWord to the Result register on the FPU. SPI:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE,[SELECTA, Result, LOADWORD,

dataHigh, dataLow, FADD0]

PC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SELECTA, Result, LOADWORD, dataHigh, dataLow,

FADD0]

```

The LOADUWORD instruction reads the two bytes following the opcode as a 16-bit unsigned integer (MSB first), converts the value to floating point, and stores the result in register 0.

## 32-bit Floating Point to Floating point

The FWRITEA, FWRITEX, and FWRITE0 instructions interpret the four bytes following the opcode as a 32-bit floating point value and stores the value in the specified register. This is one of the more efficient ways to load floating point constants, but requires knowledge of the internal representation for floating point numbers (see Appendix B). The uM-FPU V3 IDE can be used to easily generate the 32-bit values. This example sets Angle = 20.0 (the floating point representation for 20.0 is hex 41A00000). SPI:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [FWRITE, Angle, $41, $A0, $00, $00] FC:

i2cout Fpu SDA, Fpu SCL, Fpu ID, [0, FWRITE, Angle, $41, $A0, $00, $00]

```

## **ASCII string to Floating Point**

The ATOF instruction is used to convert zero-terminated strings to floating point values. The instruction reads the bytes following the opcode (until a zero terminator is read), converts the string to floating point, and stores the result in register 0. The following example sets the register Angle to 1.5885. *SPI*:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SELECTA, Angle, ATOF, "1.5885", 0, FSET0]

```

```

PC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SELECTA, Angle, ATOF, "1.5885", 0, FSET0]

```

## 8-bit Integer to Long Integer

The LSETI, LADDI, LSUBI, LMULI, LDIVI, LCMPI, LUDIVI, LUCMPI, and LTSTI instructions read the byte following the opcode as an 8-bit signed integer, convert the value to long integer, and then perform the operation. It's a convenient way to work with constants or data values that are signed 8-bit values. The following example adds the lower 8 bits of variable dataByte to the Total register on the FPU.

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SELECTA, Total, LADDI, dataByte]

FC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SELECTA, Total, LADDI, dataByte]

```

The LONGBYTE instruction reads the byte following the opcode as an 8-bit signed integer, converts the value to long integer, and stores the result in register 0.

The LONGUBYTE instruction reads the byte following the opcode as an 8-bit unsigned integer, converts the value to long integer, and stores the result in register 0.

## 16-bit Integer to Long Integer

The LONGWORD instruction reads the two bytes following the opcode as a 16-bit signed integer (MSB first), converts the value to long integer, and stores the result in register 0. The following example adds the lower 16 bits of variable dataWord to the Total register on the FPU. SPI:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SELECTA, Total, LOADWORD,

dataHigh, dataLow, LADD0]

FC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SELECTA, Total, LOADWORD, dataHigh, dataLow,

LADD0]

```

The LONGUWORD instruction reads the two bytes following the opcode as a 16-bit unsigned integer (MSB first), converts the value to long integer, and stores the result in register 0.

#### 32-bit integer to Long Integer

The LWRITE, LWRITEA, LWRITEX, and LWRITE0 instructions interpret the four bytes following the opcode as a 32-bit long integer value and stores the value in the specified register. This is used to load integer values greater than 16 bits. The *uM-FPU V3 IDE* can be used to easily generate the 32-bit values. For example, to set Total = 500000: *SPI*:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LWRITE, Total, $00, $07, $A1, $20]

PC:

i2cout Fpu SDA, Fpu SCL, Fpu ID, [0, LWRITE, Total, $00, $07, $A1, $20]

```

## **ASCII string to Long Integer**

The ATOL instruction is used to convert strings to long integer values. The instruction reads the bytes following the opcode (until a zero terminator is read), converts the string to long integer, and stores the result in register 0. The following example sets the register Total to 500000. *SPI*:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [SELECTA, Total, ATOL, "500000", 0, FSET0]

PC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, SELECTA, Total, ATOL, "500000", 0, FSET0]

```

The fastest operations occur when the FPU registers are already loaded with values. In time critical portions of code

floating point constants should be loaded beforehand to maximize the processing speed in the critical section. With 128 registers available on the FPU, it's often possible to pre-load all of the required constants. In non-critical sections of code, data and constants can be loaded as required.

## Reading Data Values from the FPU

The uM-FPU V3.1 chip has a 256 byte instruction buffer which allows data transmission to continue while previous instructions are being executed. Before reading data, you must check to ensure that the previous commands have completed, and the FPU is ready to send data. The Fpu\_Wait routine is used to wait until the FPU is ready, then a read command is sent, and the SHIFTIN or I2CREAD command is used to read data. The Fpu\_ReadDelay routine must be called before the first byte is read after a read instruction.

## 8-bit Integer

The LREADBYTE instruction reads the lower 8 bits from register A. The following example stores the lower 8 bits of register A in variable dataByte.

SPI:

```

gosub Fpu_wait

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LREADBYTE]

gosub Fpu_ReadDelay

shiftin Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [dataByte]

FC:

gosub Fpu_wait

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, LREADBYTE]

gosub Fpu_ReadDelay

i2cin Fpu_SDA, Fpu_SCL, Fpu_ID, [dataByte]

```

## 16-bit Integer

The LREADWORD instruction reads the lower 16 bits from register A. The following example stores the lower 16 bits of register A in variable dataWord.

SPI:

```

gosub Fpu_wait

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LREADWORD]

gosub Fpu_ReadDelay

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [dataHigh, dataLow]

FC:

gosub Fpu_wait

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, LREADWORD]

gosub Fpu_ReadDelay

i2cin Fpu SDA, Fpu SCL, Fpu ID, [dataHigh, dataLow]

```

#### Long Integer to ASCII string

The LTOA instruction can be used to convert long integer values to an ASCII string. The Print\_Long and Print\_LongFormat routines use this instruction to read the value from register A and send the long integer string to the terminal using the serout command.

#### Floating Point to ASCII string

The FTOA instruction can be used to convert floating point values to an ASCII string. The Print\_Float and Print\_FloatFormat routines use this instruction to read the value from register A and send the floating point string to the terminal using the serout command.

## **Comparing and Testing Floating Point Values**

Floating point values can be zero, positive, negative, infinite, or Not a Number (which occurs if an invalid operation is performed on a floating point value). The status byte is read using the Fpu\_ReadStatus routine. It waits for the FPU to be ready before sending the READSTATUS instruction and reading the status byte. The current status is returned in the fpu\_status variable. Bit definitions are provided for the status bits in the fpu\_status variable as follows:

```

fpu_status_Zero Zero status bit (0-not zero, 1-zero)

fpu_status_Sign Sign status bit (0-positive, 1-negative)

fpu_status_NaN Not a Number status bit (0-valid number, 1-NaN)

fpu_status_Inf Infinity status bit (0-not infinite, 1-infinite)

```

The FSTATUS and FSTATUSA instructions are used to set the status byte to the floating point status of the selected register. The following example checks the floating point status of register A: *SPI*:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [FSTATUSA]

PC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, FSTATUSA]

gosub Fpu_ReadStatus

if (fpu_status_Sign = 1) then

serout S_OUT, I19200, ["Result is negative"]

elseif (fpu_status_Zero = 1)

serout S_OUT, I19200, ["Result is zero"]

endif

```

The FCMP, FCMP0, and FCMP1 instructions are used to compare two floating point values. The status bits are set for the result of register A minus the operand (the selected registers are not modified). For example, to compare register A to the value 10.0:

SPI:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [FCMPI, 10]

FC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, FCMPI, 10]

gosub Fpu_ReadStatus

if (fpu_status_Zero = 1) then

serout S_OUT, I19200, ["Value1 = Value2"]

elseif (fpu_status_Sign = 1)

serout S_OUT, I19200, ["Value1 < Value2"]

else

serout S_OUT, I19200, ["Value1 > Value2"]

endif

```

The FCMP2 instruction compares two floating point registers. The status bits are set for the result of the first register minus the second register (the selected registers are not modified). For example, to compare registers Value1 and Value2:

SPI:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [FCMP2, Value1, Value2]

PC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, FCMP2, Value1, Value2]

gosub Fpu ReadStatus

```

## **Comparing and Testing Long Integer Values**

A long integer value can be zero, positive, or negative. The status byte is read using the Fpu\_Status routine. It waits for the FPU to be ready before sending the READSTATUS instruction and reading the status byte. The current status is returned in the fpu\_status variable. Bit definitions are provided for the status bits in the fpu\_status variable as follows:

```

fpu_status_Zero Zero status bit (0-not zero, 1-zero)

fpu_status_Sign Zero status bit (0-positive, 1-negative)

```

The LSTATUS and LSTATUSA instructions are used to set the status byte to the long integer status of the selected register. The following example checks the long integer status of register A: *SPI*:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LSTATUSA]

FC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, LSTATUSA]

gosub Fpu_ReadStatus

if (fpu_status_Sign = 1) then

serout S_OUT, I19200, ["Result is negative"]

elseif (fpu_status_Zero = 1)

serout S_OUT, I19200, ["Result is zero"]

endif

```

The LCMP, LCMP0, and LCMPI instructions are used to do a signed comparison of two long integer values. The status bits are set for the result of register A minus the operand (the selected registers are not modified). For example, to compare register A to the value 10:

SPI:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LCMPI, 10]

PC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, LCMPI, 10]

gosub Fpu_ReadStatus

if (fpu_status_Zero = 1) then

serout S_OUT, I19200, ["Value1 = Value2"]

elseif (fpu_status_Sign = 1)

serout S_OUT, I19200, ["Value1 < Value2"]

else

serout S_OUT, I19200, ["Value1 > Value2"]

endif

```

The LCMP2 instruction does a signed compare of two long integer registers. The status bits are set for the result of the first register minus the second register (the selected registers are not modified). For example, to compare registers Value1 and Value2:

SPI:

```

shiftout Fpu_SIN, Fpu_SCLK, FASTMSBPRE, [LCMP2, Value1, Value2]

PC:

i2cout Fpu_SDA, Fpu_SCL, Fpu_ID, [0, LCMP2, Value1, Value2]

gosub Fpu_ReadStatus

```

The LUCMP, LUCMPO, and LUCMPI instructions are used to do an unsigned comparison of two long integer values. The status bits are set for the result of register A minus the operand (the selected registers are not modified).

The LUCMP2 instruction does an unsigned compare of two long integer registers. The status bits are set for the result of the first register minus the second register (the selected registers are not modified).

The LTST, LTSTO and LTSTI instructions are used to do a bit-wise compare of two long integer values. The status bits are set for the logical AND of register A and the operand (the selected registers are not modified).

## **Further Information**

The following documents are also available:

uM-FPU V3.1 Datasheetprovides hardware details and specificationsuM-FPU V3.1 Instruction Referenceprovides detailed descriptions of each instructionuM-FPU Application Notesvarious application notes and examples

Check the Micromega website at www.micromegacorp.com for up-to-date information.

# Appendix A uM-FPU V3.1 Instruction Summary

| Instruction | Opcod | le Arguments   | Returns     | Description                             |

|-------------|-------|----------------|-------------|-----------------------------------------|

| NOP         | 00    |                |             | No Operation                            |

| SELECTA     | 01    | nn             |             | Select register A                       |

| SELECTX     | 02    | nn             |             | Select register X                       |

| CLR         | 03    | nn             |             | reg[nn] = 0                             |

| CLRA        | 04    |                |             | reg[A] = 0                              |

| CLRX        | 05    |                |             | reg[X] = 0, X = X + 1                   |

| CLR0        | 06    |                |             | reg[nn] = 0                             |

| COPY        | 07    | mm,nn          |             | reg[nn] = reg[mm]                       |

| COPYA       | 08    | nn             |             | reg[nn] = reg[A]                        |

| COPYX       | 09    | nn             |             | reg[nn] = reg[X], X = X + 1             |

| LOAD        | 0A    | nn             |             | reg[0] = reg[nn]                        |

| LOADA       | 0В    |                |             | reg[0] = reg[A]                         |

| LOADX       | 0C    |                |             | reg[0] = reg[X], X = X + 1              |

| ALOADX      | 0D    |                |             | reg[A] = reg[X], X = X + 1              |

| XSAVE       | 0E    | nn             |             | reg[X] = reg[nn], X = X + 1             |

| XSAVEA      | 0F    |                |             | reg[X] = reg[A], X = X + 1              |

| COPY0       | 10    | nn             |             | reg[nn] = reg[0]                        |

| COPYI       | 11    | bb,nn          |             | reg[nn] = long(unsigned byte bb)        |

| F_SWAP      | 12    | nn,mm          |             | Swap reg[nn] and reg[mm]                |

| SWAPA       | 13    | nn             |             | Swap reg[A] and reg[nn]                 |

| LEFT        | 14    |                |             | Left parenthesis                        |

| RIGHT       | 15    |                |             | Right parenthesis                       |

| FWRITE      | 16    | nn,b1,b2,b3,b4 |             | Write 32-bit floating point to reg[nn]  |

| FWRITEA     | 17    | b1,b2,b3,b4    |             | Write 32-bit floating point to reg[A]   |

| FWRITEX     | 18    | b1,b2,b3,b4    |             | Write 32-bit floating point to reg[X]   |

| FWRITE0     | 19    | b1,b2,b3,b4    |             | Write 32-bit floating point to reg[0]   |

| FREAD       | 1A    | nn             | b1,b2,b3,b4 | Read 32-bit floating point from reg[nn] |

| FREADA      | 1в    |                | b1,b2,b3,b4 | Read 32-bit floating point from reg[A]  |

| FREADX      | 1C    |                | b1,b2,b3,b4 | Read 32-bit floating point from reg[X]  |

| FREAD0      | 1C    |                | b1,b2,b3,b4 | Read 32-bit floating point from reg[0]  |

| ATOF        | 1E    | aa00           |             | Convert ASCII to floating point         |

| FTOA        | 1F    | bb             |             | Convert floating point to ASCII         |

| FSET        | 20    | nn             |             | reg[A] = reg[nn]                        |

| F_FADD      | 21    | nn             |             | reg[A] = reg[A] + reg[nn]               |

| F_FSUB      | 22    | nn             |             | reg[A] = reg[A] - reg[nn]               |

| FSUBR       | 23    | nn             |             | reg[A] = reg[nn] - reg[A]               |

| F_FMUL      | 24    | nn             |             | reg[A] = reg[A] * reg[nn]               |

| F_FDIV      | 25    | nn             |             | reg[A] = reg[A] / reg[nn]               |

| FDIVR       | 26    | nn             |             | reg[A] = reg[nn] / reg[A]               |

| FPOW        | 27    | nn             |             | reg[A] = reg[A] ** reg[nn]              |

| FCMP        | 28    | nn             |             | Compare reg[A], reg[nn],                |

|             |       |                |             | Set floating point status               |

| FSET0       | 29    |                |             | reg[A] = reg[0]                         |

| FADD0       | 2A    |                |             | reg[A] = reg[A] + reg[0]                |

| FSUB0       | 2В    |                |             | reg[A] = reg[A] - reg[0]                |

| FSUBR0   | 2C    |            | reg[A] = reg[0] - reg[A]                                                          |

|----------|-------|------------|-----------------------------------------------------------------------------------|

| FMUL0    | 2D    |            | reg[A] = reg[A] * reg[0]                                                          |

| FDIV0    | 2E    |            | reg[A] = reg[A] / reg[0]                                                          |

| FDIVR0   | 2F    |            | reg[A] = reg[O] / reg[A]                                                          |

| FPOW0    | 30    |            | reg[A] = reg[A] ** reg[0]                                                         |

| FCMP0    | 31    |            | Compare reg[A], reg[0],                                                           |

| FCMPU    | 31    |            | Set floating point status                                                         |

| FSETI    | 32    | bb         | reg[A] = float(bb)                                                                |

| FADDI    | 33    | bb         | reg[A] = reg[A] - float(bb)                                                       |

| FSUBI    | 34    | bb         | reg[A] = reg[A] - float(bb)                                                       |

| FSUBRI   | 35    | bb         | reg[A] = float(bb) - reg[A]                                                       |

| FMULI    | 36    | bb         | reg[A] = reg[A] * float(bb)                                                       |

| FDIVI    | 37    | bb         | reg[A] = reg[A] / float(bb)                                                       |

| FDIVRI   | 38    | bb         | reg[A] = float(bb) / reg[A]                                                       |

| FPOWI    | 39    | bb         | reg[A] = reg[A] ** bb                                                             |

| FCMPI    | 3A    | bb         | Compare reg[A], float(bb),                                                        |

| FCMPI    | JA.   | da         | Set floating point status                                                         |

| FSTATUS  | 3B    | nn         | Set floating point status  Set floating point status for reg[nn]                  |

| FSTATUSA | 3C    | 11111      | Set floating point status for reg[A]                                              |

| FCMP2    | 3D    | nn,mm      | Compare reg[nn], reg[mm]                                                          |

| T CMF Z  | المرا | 1111,11111 | Set floating point status                                                         |

| F FNEG   | 3E    |            | reg[A] = -reg[A]                                                                  |

| FABS     | 3F    |            | reg[A] = I reg[A] I                                                               |

| FINV     | 40    |            | reg[A] = 1 / reg[A]                                                               |

| SQRT     | 41    |            | reg[A] = sqrt(reg[A])                                                             |

| ROOT     | 42    | nn         | reg[A] = root(reg[A], reg[nn])                                                    |

| LOG      | 43    |            | reg[A] = log(reg[A])                                                              |

| LOG10    | 44    |            | reg[A] = log10(reg[A])                                                            |

| EXP      | 45    |            | reg[A] = exp(reg[A])                                                              |

| EXP10    | 46    |            | reg[A] = exp10(reg[A])                                                            |

| F SIN    | 47    |            | reg[A] = sin(reg[A])                                                              |

| F COS    | 48    |            | reg[A] = cos(reg[A])                                                              |

| F TAN    | 49    |            | reg[A] = tan(reg[A])                                                              |

| ASIN     | 4A    |            | reg[A] = asin(reg[A])                                                             |

| ACOS     | 4B    |            | reg[A] = acos(reg[A])                                                             |

| ATAN     | 4C    |            | reg[A] = atan(reg[A])                                                             |

| ATAN2    | 4D    | nn         | reg[A] = atan2(reg[A], reg[nn])                                                   |

| DEGREES  | 4E    |            | reg[A] = degrees(reg[A])                                                          |

| RADIANS  | 4F    |            | reg[A] = radians(reg[A])                                                          |

| FMOD     | 50    | nn         | reg[A] = reg[A] MOD reg[nn]                                                       |

| FLOOR    | 51    | <u> </u>   | reg[A] = floor(reg[A])                                                            |

| CEIL     | 52    |            | reg[A] = ceil(reg[A])                                                             |

| ROUND    | 53    |            | reg[A] = round(reg[A])                                                            |

| FMIN     | 54    | nn         | reg[A] = min(reg[A], reg[nn])                                                     |

| FMAX     | 55    | nn         | reg[A] = max(reg[A], reg[nn])                                                     |

| FCNV     | 56    | bb         | reg[A] = conversion(bb, reg[A])                                                   |

| FMAC     | 57    | +          | reg[A] = conversion(bb, reg[A])  reg[A] = reg[A] + (reg[nn] * reg[mm])            |

| FMAC     | _     | nn,mm      | reg[A] = reg[A] + (reg[riri] - reg[ririi])  reg[A] = reg[A] - (reg[nn] * reg[mm]) |

|          | 58    | nn,mm      |                                                                                   |

| LOADBYTE | 59    | bb         | reg[0] = float(signed bb)                                                         |

| LOADUBYTE | 5A | bb             | 1           | reg[0] = float(unsigned byte)                          |

|-----------|----|----------------|-------------|--------------------------------------------------------|

| LOADWORD  | 5B | b1,b2          |             | reg[0] = float(signed b1*256 + b2)                     |

| LOADUWORD | 5C | b1,b2          |             | reg[0] = float(unsigned b1*256 + b2)                   |

| LOADE     | 5D | D1, D2         |             | reg[0] = 2.7182818                                     |

| LOADPI    | 5E |                |             | reg[0] = 3.1415927                                     |

| LOADCON   | 5F | bb             | 1           | reg[0] = 5.1413927<br>reg[0] = float constant(bb)      |

| F FLOAT   | 60 | ממ             | 1           | reg[A] = float(reg[A])                                 |

| FIX       | 61 |                | 1           | reg[A] = float(reg[A])                                 |

|           | 62 |                | +           | reg[A] = fix(reg[A])<br>reg[A] = fix(round(reg[A]))    |

| FIXR      |    |                |             | reg[A] = fix(found(reg[A]))                            |

| FRAC      | 63 |                | 1           |                                                        |

| FSPLIT    | 64 |                |             | reg[A] = integer(reg[A]),<br>reg[0] = fraction(reg[A]) |

| SELECTMA  | 65 | nn,b1,b2       |             | Select matrix A                                        |

| SELECTMB  | 66 | nn,b1,b2       |             | Select matrix B                                        |

| SELECTMC  | 67 | nn,b1,b2       |             | Select matrix C                                        |

| LOADMA    | 68 | b1,b2          |             | reg[0] = Matrix A[bb, bb]                              |

| LOADMB    | 69 | b1,b2          |             | reg[0] = Matrix B[bb, bb]                              |

| LOADMC    | 6A | b1,b2          |             | reg[0] = Matrix C[bb, bb]                              |

| SAVEMA    | 6B | b1,b2          |             | Matrix A[bb, bb] = reg[A]                              |

| SAVEMB    | 6C | b1,b2          |             | Matrix B[bb, bb] = reg[A]                              |

| SAVEMC    | 6D | b1,b2          |             | Matrix C[bb, bb] = reg[A]                              |

| MOP       | 6E | bb             |             | Matrix/Vector operation                                |

| FFT       | 6F | bb             |             | Fast Fourier Transform                                 |

| WRBLK     | 70 | tc t1tn        |             | Write multiple 32-bit values                           |

| RDBLK     | 71 | tc             | t1tn        | Read multiple 32-bit values                            |

| LOADIND   | 7A | nn             |             | reg[0] = reg[reg[nn]]                                  |

| SAVEIND   | 7В | nn             |             | reg[reg[nn]] = reg[A]                                  |

| INDA      | 7C | nn             |             | Select register A using value in reg[nn]               |

| INDX      | 7D | nn             |             | Select register X using value in reg[nn]               |

| FCALL     | 7E | bb             |             | Call user-defined function in Flash                    |

| EECALL    | 7F | bb             |             | Call user-defined function in EEPROM                   |

| RET       | 80 |                |             | Return from user-defined function                      |

| BRA       | 81 | bb             |             | Unconditional branch                                   |

| BRA       | 82 | cc, bb         |             | Conditional branch                                     |

| JMP       | 83 | b1, b2         |             | Unconditional jump                                     |

| JMP       | 84 | cc, b1, b2     |             | Conditional jump                                       |

| TABLE     | 85 | tc, t0tn       | 1           | Table lookup                                           |

| FTABLE    | 86 | cc,tc,t0tn     |             | Floating point reverse table lookup                    |

| LTABLE    | 87 | cc,tc,t0tn     | 1           | Long integer reverse table lookup                      |

| POLY      | 88 | tc,t0tn        | 1           | reg[A] = nth order polynomial                          |

| F GOTO    | 89 | nn             |             | Computed GOTO                                          |

| LWRITE    | 90 | nn,b1,b2,b3,b4 |             | Write 32-bit long integer to reg[nn]                   |

| LWRITEA   | 91 | b1,b2,b3,b4    | 1           | Write 32-bit long integer to reg[A]                    |

| LWRITEX   | 92 | b1,b2,b3,b4    |             | Write 32-bit long integer to reg[X],                   |

|           | -  | , , -,         |             | X = X + 1                                              |

| LWRITE0   | 93 | b1,b2,b3,b4    |             | Write 32-bit long integer to reg[0]                    |

| LREAD     | 94 | nn             | b1,b2,b3,b4 | Read 32-bit long integer from reg[nn]                  |

| LREADA    | 95 |                | b1,b2,b3,b4 | Read 32-bit long value from reg[A]                     |

| LREADX    | 96   |      | b1,b2,b3,b4 | Read 32-bit long integer from reg[X],<br>X = X + 1 |

|-----------|------|------|-------------|----------------------------------------------------|

| LREAD0    | 97   |      | b1,b2,b3,b4 | Read 32-bit long integer from reg[0]               |

| LREADBYTE | 98   |      | bb          | Read lower 8 bits of reg[A]                        |

| LREADWORD | 99   |      | b1,b2       | Read lower 16 bits reg[A]                          |

|           |      | 00   | D1, D2      | <u> </u>                                           |

| ATOL      | 9A   | aa00 |             | Convert ASCII to long integer                      |

| LTOA      | 9B   | bb   |             | Convert long integer to ASCII                      |

| LSET      | 9C   | nn   |             | reg[A] = reg[nn]                                   |

| LADD      | 9D   | nn   |             | reg[A] = reg[A] + reg[nn]                          |

| LSUB      | 9E   | nn   |             | reg[A] = reg[A] - reg[nn]                          |

| LMUL      | 9F   | nn   |             | reg[A] = reg[A] * reg[nn]                          |

| LDIV      | A0   | nn   |             | reg[A] = reg[A] / reg[nn]<br>reg[0] = remainder    |

| LCMP      | A1   | nn   |             | Signed compare reg[A] and reg[nn],                 |

| LCMF      | A    |      |             | Set long integer status                            |

| LUDIV     | A2   | nn   |             | reg[A] = reg[A] / reg[nn]                          |

| HODIV     | AZ   |      |             | reg[0] = remainder                                 |

| LUCMP     | A3   | nn   |             | Unsigned compare reg[A] and reg[nn],               |

| Пости     | 113  |      |             | Set long integer status                            |

| LTST      | A4   | nn   |             | Test reg[A] AND reg[nn],                           |

|           | 1114 | 1    |             | Set long integer status                            |

| LSET0     | A5   |      |             | reg[A] = reg[0]                                    |

| LADD0     | A6   |      |             | reg[A] = reg[A] + reg[0]                           |

| LSUB0     | A7   |      |             | reg[A] = reg[A] - reg[0]                           |

| LMUL0     | A8   |      |             | reg[A] = reg[A] * reg[0]                           |

| LDIV0     | A9   |      |             | reg[A] = reg[A] / reg[0]                           |

| LDIVO     | A    |      |             | reg[0] = remainder                                 |

| LCMP0     | AA   |      |             | Signed compare reg[A] and reg[0],                  |

|           |      |      |             | set long integer status                            |

| LUDIV0    | AB   |      |             | reg[A] = reg[A] / reg[0]                           |

|           |      |      |             | reg[0] = remainder                                 |

| LUCMP0    | AC   |      |             | Unsigned compare reg[A] and reg[0],                |

|           |      |      |             | Set long integer status                            |

| LTST0     | AD   |      |             | Test reg[A] AND reg[0],                            |

|           |      |      |             | Set long integer status                            |

| LSETI     | AE   | bb   |             | reg[A] = long(bb)                                  |

| LADDI     | AF   | bb   |             | reg[A] = reg[A] + long(bb)                         |

| LSUBI     | в0   | bb   |             | reg[A] = reg[A] - long(bb)                         |

| LMULI     | В1   | bb   |             | reg[A] = reg[A] * long(bb)                         |

| LDIVI     | B2   | bb   |             | reg[A] = reg[A] / long(bb)                         |

|           |      |      |             | reg[0] = remainder                                 |

| LCMPI     | В3   | bb   |             | Signed compare reg[A] - long(bb),                  |

|           |      |      |             | Set long integer status                            |

| LUDIVI    | В4   | bb   |             | reg[A] = reg[A] / unsigned long(bb)                |

| _         |      |      |             | reg[0] = remainder                                 |

| LUCMPI    | В5   | bb   |             | Unsigned compare reg[A] and long(bb),              |

|           |      |      |             | Set long integer status                            |

| LTSTI     | В6   | bb   |             | Test reg[A] AND long(bb),                          |

|           |      |      |             | Set long integer status                            |

| LSTATUS   | В7   | nn   |             | Set long integer status for reg[nn]                |

| LSTATUSA  | В8 |            | Set long integer status for reg[A]                             |

|-----------|----|------------|----------------------------------------------------------------|

| LCMP2     | В9 | nn,mm      | Signed long compare reg[nn], reg[mm] Set long integer status   |

| LUCMP2    | BA | nn,mm      | Unsigned long compare reg[nn], reg[mm] Set long integer status |

| LNEG      | ВВ |            | reg[A] = -reg[A]                                               |

| LABS      | BC |            | reg[A] = I reg[A] I                                            |

| LINC      | BD | nn         | reg[nn] = reg[nn] + 1, set status                              |

| LDEC      | BE | nn         | reg[nn] = reg[nn] - 1, set status                              |

| LNOT      | BF |            | reg[A] = NOT reg[A]                                            |

| LAND      | C0 | nn         | reg[A] = reg[A] AND reg[nn]                                    |

| LOR       | C1 | nn         | reg[A] = reg[A] OR reg[nn]                                     |

| LXOR      | C2 | nn         | reg[A] = reg[A] XOR reg[nn]                                    |

| LSHIFT    | C3 | nn         | reg[A] = reg[A] shift reg[nn]                                  |

| LMIN      | C4 | nn         | reg[A] = min(reg[A], reg[nn])                                  |

| LMAX      | C5 | nn         | reg[A] = max(reg[A], reg[nn])                                  |

| LONGBYTE  | C6 | bb         | reg[0] = long(signed byte bb)                                  |

| LONGUBYTE | C7 | bb         | reg[0] = long(unsigned byte bb)                                |

| LONGWORD  | C8 | b1,b2      | reg[0] = long(signed b1*256 + b2)                              |

| LONGUWORD | C9 | b1,b2      | reg[0] = long(unsigned b1*256 + b2)                            |

| SETSTATUS | CD | SS         | Set status byte                                                |

| F SEROUT  | CE | bb         | Serial output                                                  |

| _BEROOT   |    | bb bd      | Condi odiput                                                   |

|           |    | bb aa00    |                                                                |

| F SERIN   | CF | bb         | Serial input                                                   |

| SETOUT    | D0 | bb         | Set OUT1 and OUT2 output pins                                  |

| ADCMODE   | D1 | bb         | Set A/D trigger mode                                           |

| ADCTRIG   | D2 |            | A/D manual trigger                                             |

| ADCSCALE  | D3 | ch         | ADCscale[ch] = B                                               |

| ADCLONG   | D4 | ch         | reg[0] = ADCvalue[ch]                                          |

| ADCLOAD   | D5 | ch         | reg[0] = float(ADCvalue[ch]) * ADCscale[ch]                    |

| ADCWAIT   | D6 |            | wait for next A/D sample                                       |

| TIMESET   | D7 |            | time = reg[0]                                                  |

| TIMELONG  | D8 |            | reg[0] = time (long integer)                                   |

| TICKLONG  | D9 |            | reg[0] = ticks (long integer)                                  |

| EESAVE    | DA | mm,nn      | EEPROM[nn] = reg[mm]                                           |

| EESAVEA   | DB | nn         | EEPROM[nn] = reg[A]                                            |

| EELOAD    | DC | mm,nn      | reg[mm] = EEPROM[nn]                                           |

| EELOADA   | DD | nn         | reg[A] = EEPROM[nn]                                            |

| EEWRITE   | DE | nn,bc,b1bn | Store bytes in EEPROM                                          |

| EXTSET    | E0 |            | external input count = reg[0]                                  |

| EXTLONG   | E1 |            | reg[0] = external input counter                                |

| EXTWAIT   | E2 |            | wait for next external input                                   |

| STRSET    | E3 | aa00       | Copy string to string buffer                                   |

| STRSEL    | E4 | bb, bb     | Set selection point                                            |

| STRINS    | E5 | aa00       | Insert string at selection point                               |

| STRCMP    | E6 | aa00       | Compare string with string buffer                              |

| STRFIND   | E7 | aa00       | Find string and set selection point                            |

| STRFCHR    | E8 | aa00 |      | Set field separators                                                |

|------------|----|------|------|---------------------------------------------------------------------|

| STRFIELD   | E9 | bb   |      | Find field and set selection point                                  |

| STRTOF     | EA |      |      | Convert selected string to floating point                           |

| STRTOL     | EB |      |      | Convert selected string to long integer                             |

| READSEL    | EC |      | aa00 | Read selected string                                                |

| STRBYTE    | ED | bb   |      | Insert byte at selection point                                      |

| STRINC     | EE |      |      | Increment string selection point                                    |

| STRDEC     | EF |      |      | Decrement string selection point                                    |

| F_SYNC     | F0 |      | 5C   | Get synchronization byte                                            |

| READSTATUS | F1 |      | ss   | Read status byte                                                    |

| READSTR    | F2 |      | aa00 | Read string from string buffer                                      |

| VERSION    | F3 |      |      | Copy version string to string buffer                                |

| IEEEMODE   | F4 |      |      | Set IEEE mode (default)                                             |

| PICMODE    | F5 |      |      | Set PIC mode                                                        |

| CHECKSUM   | F6 |      |      | Calculate checksum for uM-FPU code                                  |

| BREAK      | F7 |      |      | Debug breakpoint                                                    |

| TRACEOFF   | F8 |      |      | Turn debug trace off                                                |

| TRACEON    | F9 |      |      | Turn debug trace on                                                 |

| TRACESTR   | FA | aa00 |      | Send string to debug trace buffer                                   |

| TRACEREG   | FB | nn   |      | Send register value to trace buffer                                 |

| READVAR    | FC | nn   |      | Read internal register value                                        |

| RESET      | FF |      |      | Reset (9 consecutive FF bytes cause a reset, otherwise it is a NOP) |

Notes: Opcode Instruction opcode in hexadecimal Arguments Additional data required by instruction

> Returns Data returned by instruction register number (0-127) nn register number (0-127) mm function number (0-63) fn

8-bit value

b1,b2 16-bit value (b1 is MSB) b1, b2, b3, b4 32-bit value (b1 is MSB) string of 8-bit bytes b1...bn

Status byte SS

baud rate and debug mode bd

Condition code CC

EEPROM address slot (0-255) ee

ch A/D channel number

bc Byte count

tc 32-bit value count String of 32-bit values t1...tn

aa...00 Zero terminated ASCII string

The SWAP, FADD, FSUB, FMUL, FDIV, FNEG, SIN, COS, TAN, FLOAT, GOTO, SEROUT, SERIN and SYNC opcodes have been renamed to include an F\_ prefix (e.g. F\_SIN, F\_COS, etc.) to avoid conflicts with BasicATOM reserved names.

## Appendix B Floating Point Numbers

Floating point numbers can store both very large and very small values by "floating" the window of precision to fit the scale of the number. Fixed point numbers can't handle very large or very small numbers and are prone to loss of precision when numbers are divided. The representation of floating point numbers used by the uM-FPU V3.1 is defined by the 32-bit IEEE 754 standard. The number of significant digits for a 32-bit floating point number is slightly more than 7 digits, and the range of values that can be handled is approximately  $\pm 10^{38.53}$ .

## 32-bit IEEE 754 Floating Point Representation

IEEE 754 floating point numbers have three components: a sign, exponent, the mantissa. The sign indicates whether the number is positive or negative. The exponent has an implied base of two and a bias value. The mantissa represents the fractional part of the number.

The 32-bit IEEE 754 representation is as follows:

| Bit 3 | 1 30 | 23       | 22 0     |

|-------|------|----------|----------|

| [5    |      | Exponent | Mantissa |

## Sign Bit (bit 31)

The sign bit is 0 for a positive number and 1 for a negative number.

## Exponent (bits 30-23)

The exponent field is an 8-bit field that stores the value of the exponent with a bias of 127 that allows it to represent both positive and negative exponents. For example, if the exponent field is 128, it represents an exponent of one (128 - 127 = 1). An exponent field of all zeroes is used for denormalized numbers and an exponent field of all ones is used for the special numbers +infinity, -infinity and Not-a-Number (described below).

#### Mantissa (bits 30-23)

The mantissa is a 23-bit field that stores the precision bits of the number. For normalized numbers there is an implied leading bit equal to one.

## **Special Values**

## Zero

A zero value is represented by an exponent of zero and a mantissa of zero. Note that +0 and -0 are distinct values although they compare as equal.

## Denormalized

If an exponent is all zeros, but the mantissa is non-zero the value is a denormalized number. Denormalized numbers are used to represent very small numbers and provide for an extended range and a graceful transition towards zero on underflows. Note: The uM-FPU does not support operations using denormalized numbers.

## Infinity

The values +infinity and -infinity are denoted with an exponent of all ones and a fraction of all zeroes. The sign bit distinguishes between +infinity and -infinity. This allows operations to continue past an overflow. A nonzero number divided by zero will result in an infinity value.

## Not A Number (NaN)

The value NaN is used to represent a value that does not represent a real number. An operation such as zero divided by zero will result in a value of NaN. The NaN value will flow through any mathematical operation. Note: The uM-FPU initializes all of its registers to NaN at reset, therefore any operation that uses a register that has not been previously set with a value will produce a result of NaN.

Some examples of 32-bit IEEE 754 floating point values displayed as four 8-bit hexadecimal constants are as follows:

```

$00, $00, $00, $00

' 0.0

$3D, $CC, $CC, $CD

' 0.1

$3F, $00, $00, $00

' 0.5

$3F, $40, $00, $00

' 0.75

' 0.9999

$3F, $7F, $F9, $72

' 1.0

$3F, $80, $00, $00

' 2.0

$40, $00, $00, $00

$40, $2D, $F8, $54

' 2.7182818 (e)

$40, $49, $0F, $DB

' 3.1415927 (pi)

' 10.0

$41, $20, $00, $00

' 100.0

$42, $C8, $00, $00

' 1000.0

$44, $7A, $00, $00

' 1234.5678

$44, $9A, $52, $2B

$49, $74, $24, $00

' 1000000.0

$80, $00, $00, $00

' -0.0

$BF, $80, $00, $00

' -1.0

$C1, $20, $00, $00

' -10.0

$C2, $C8, $00, $00

' -100.0

$7F, $C0, $00, $00

' NaN (Not-a-Number)

' +inf

$7F, $80, $00, $00

' -inf

$FF, $80, $00, $00

```

Note: The Basic ATOM uses a modified version of the 32-bit IEEE floating point format. The uM-FPU PICMODE instruction can be used to set a mode for reading and writing this alternate floating point format, but in most applications the data transferred between the Basic ATOM and the FPU will be integer or ASCII.